SOLVED: Design a four-bit binary counter using Verilog (using loop or switch statement) with explaination.

Verilog Synthesizers - Introduction to Digital Systems Design - Solved Exams | Exams Digital Systems Design | Docsity

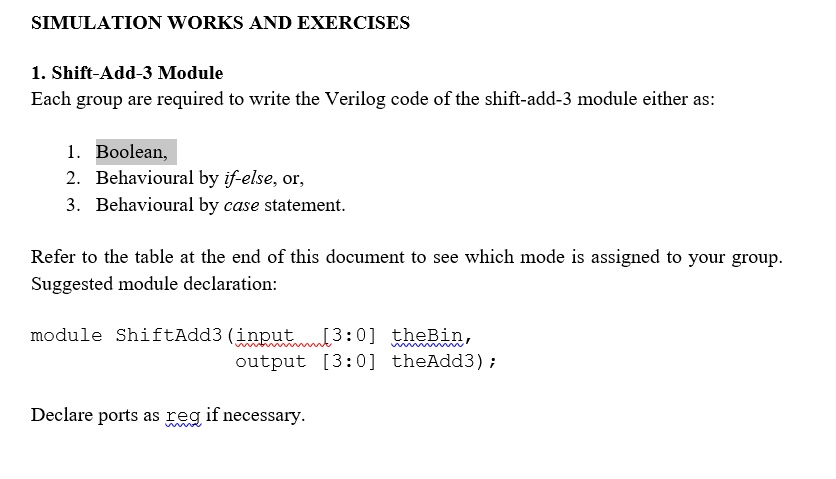

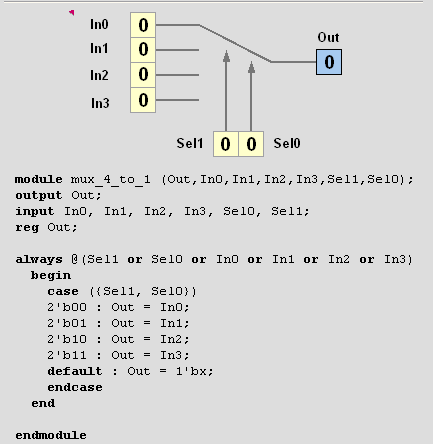

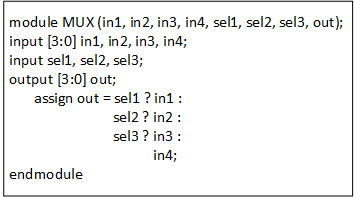

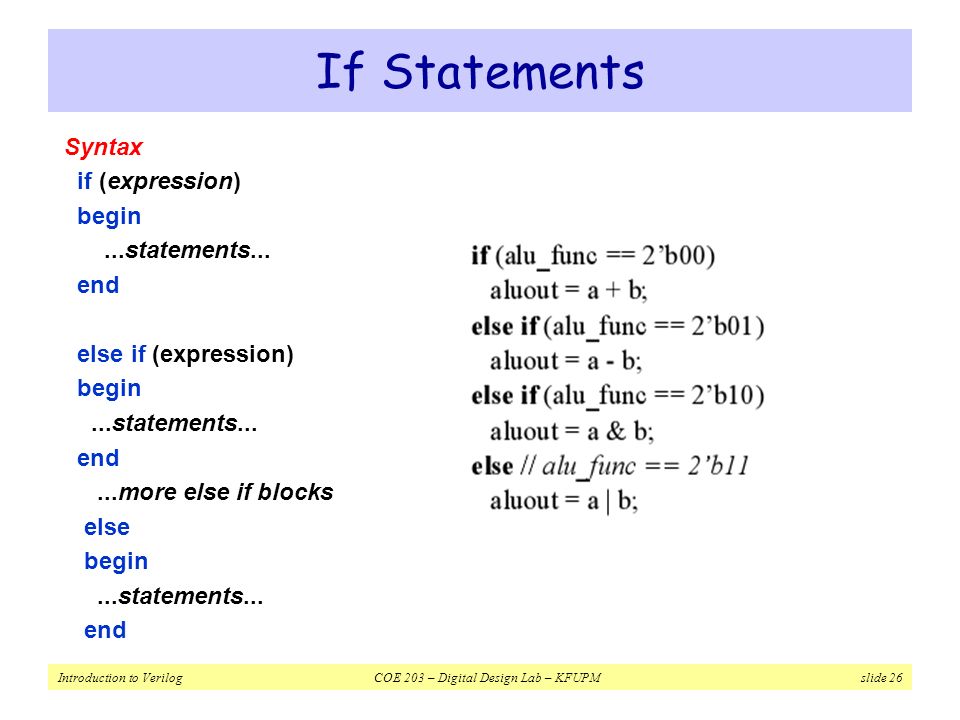

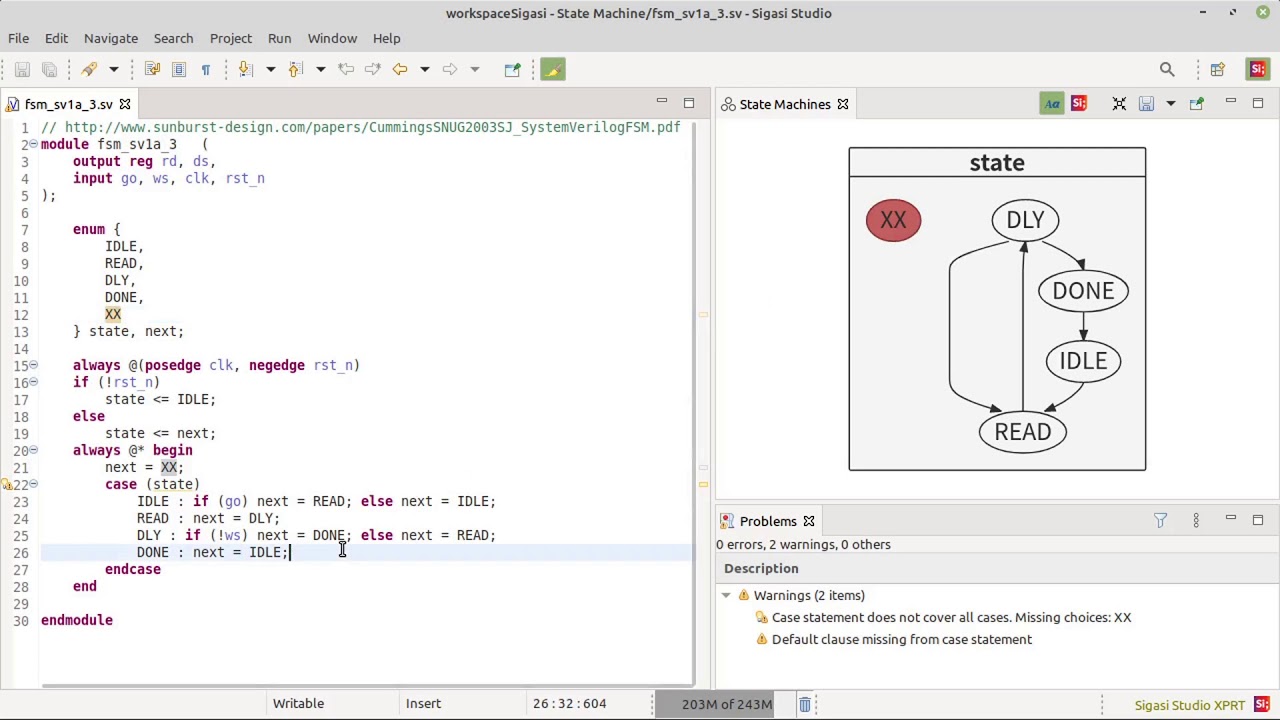

Use Verilog to Describe a Combinational Circuit: The “If” and “Case” Statements - Technical Articles

![PDF] Design of a Switch-Level Analog Model for Verilog | Semantic Scholar PDF] Design of a Switch-Level Analog Model for Verilog | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/a167f918c947c3a435b639b120ca5eb2c256039f/5-Figure12-1.png)